# μ**A9708**

# 6-CHANNEL, 8-BIT, MICROPROCESSOR COMPATIBLE

ANALOG-TO-DIGITAL CONVERTER SUBSYSTEM\*

FAIRCHILD LINEAR INTEGRATED CIRCUITS

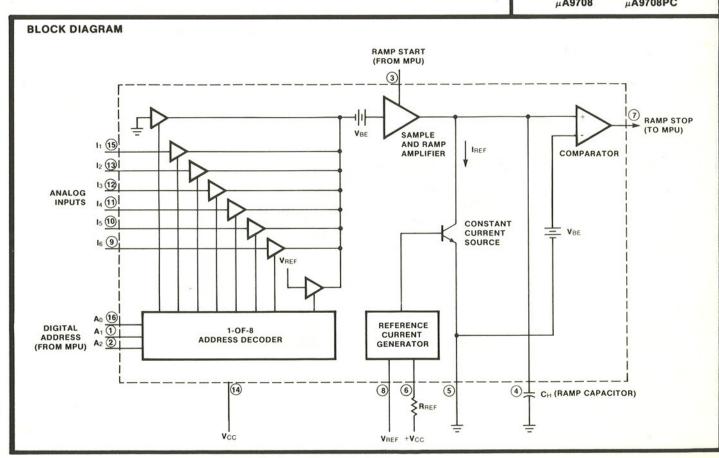

**GENERAL DESCRIPTION** — The  $\mu$ A9708 is a single slope 8-bit, 6-channel ADC subsystem that provides all of the necessary analog functions for a microprocessor-based data control system. The device uses a microprocessor system like the F3870 or F6800 to provide the necessary addressing, timing and counting functions and includes a 1 of 8 decoder, 8-channel analog multiplexer, sample and hold, ramp integrator, precision ramp reference, and a comparator on a single monolithic chip.

- MPU COMPATIBLE

- EXCELLENT LINEARITY OVER FULL TEMP RANGE ±0.2% MAX

- TYPICAL 300 μs CONVERSION TIME PER CHANNEL

- WIDE DYNAMIC RANGE INCLUDES GROUND

- AUTO-ZERO AND FULL-SCALE CORRECTION CAPABILITY

- RATIOMETRIC CONVERSION NO PRECISION REFERENCE REQUIRED

- SINGLE-SUPPLY OPERATION

- TTL COMPATIBLE

- DOES NOT REQUIRE ACCESS TO DATA BUS OR ADDRESS BUS

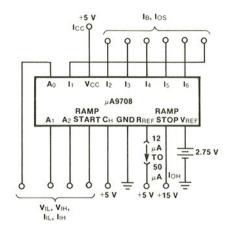

#### CONNECTION DIAGRAM 16-PIN DUAL IN-LINE (TOP VIEW) PACKAGE OUTLINES 7B 9B PACKAGE CODES 16 Ao A1 [ A2 🗌 11 15 RAMP START -☐ Vcc 12 GND [ ☐ I<sub>3</sub> 12 11 14 RREF RAMP STOP -10 Is ORDER INFORMATION TYPE PART NO. μ**A9708** μA9708DM μ**A9708** μA9708DC μA9708PC μ**A9708**

e1978 Fairchild Camera and Instrument Corporation Printed in U.S.A.

234-11-0016-118 15M

# FAIRCHILD • μA9708

## **ABSOLUTE MAXIMUM RATINGS**

18 V Supply Voltage (Vcc) Comparator Output (Ramp Stop) -0.3 V to +18 V Analog Input Range -0.3 V to 30 V -0.3 V to 30 V Digital Input Range 10 mA **Output Sink Current** Operating Temperature Range 0°C to 70°C μA9708PC, μA9708DC -55° C to 125° C μA9708DM Storage Temperature Range -65° C to +150° C Continuous Total Dissipation 900 mW Ceramic DIP Package 1000 mW Plastic DIP Package 300° C Pin Temperature, Ceramic DIP (Soldering, 60 s) 260° C Plastic DIP (Soldering, 10 s)

# RECOMMENDED OPERATING CONDITIONS

| CHARACTERISTICS             | MIN  | TYP         | MAX  | UNITS |

|-----------------------------|------|-------------|------|-------|

| Supply Voltage (Vcc)        | 4.75 | 5.0         | 15   | V     |

| Reference Voltage (VREF)*   | 2.8  |             | 5.25 | V     |

| Ramp Capacitor (CH)         | 300  |             |      | pF    |

| Reference Current (IR)      | 12   |             | 50   | μΑ    |

| Analog Input Range          | 0    |             | VREF | V     |

| Ramp Stop Output<br>Current |      | in a second | 1.6  | mA -  |

<sup>\*2</sup> V ≤ VREF ≤ (VCC -2 V)

## **CHANNEL SELECTION**

| NPUT ADDRESS LINE |                |    | SELECTED       |  |

|-------------------|----------------|----|----------------|--|

| A <sub>2</sub>    | A <sub>1</sub> | Ao | ANALOG INPUT   |  |

| 0                 | 0              | 0  | Ground         |  |

| 0                 | 0              | 1  | l <sub>1</sub> |  |

| 0                 | 1              | 0  | 12             |  |

| 0                 | 1              | 1  | 13             |  |

| 1                 | 0              | 0  | 14             |  |

| 1                 | 0              | 1  | 15             |  |

| 1                 | 1              | 0  | 16             |  |

| 1                 | - 1            | 1  | VREF           |  |

## FAIRCHILD • µA9708

**ELECTRICAL CHARACTERISTICS:** Over recommended operating conditions, -55° C  $\leq$  T<sub>A</sub>  $\leq$  +125° C, for  $\mu$ A9708DM and 0° C  $\leq$  T<sub>A</sub>  $\leq$  +70° C for  $\mu$ A9708DC or  $\mu$ A9708PC; unless otherwise specified.

| 0                                           | SYMBOL         | CONDITIONS                                                                     | LIMITS |       |      | UNITS |

|---------------------------------------------|----------------|--------------------------------------------------------------------------------|--------|-------|------|-------|

| CHARACTERISTICS                             | SYMBOL         | CONDITIONS                                                                     | MIN    | TYP   | MAX  | ONTE  |

| Conversion Accuracy                         | EA             | Over entire temperature range (Note 1)                                         |        | ±0.2  | ±0.3 | %     |

| Linearity                                   | ER             | Applies to any one channel (Note 2)                                            |        | ±0.08 | ±0.2 | %     |

| Multiplexer Input Offset Voltage            | Vosm           | Channel ON                                                                     | 4.0    | 2.0   | 4.0  | mV    |

| Conversion Time Per Channel                 | tc             | Analog Input = 0v to VREF<br>C <sub>H</sub> = 300 pF, I <sub>REF</sub> = 50 μA |        | 296   | 350  | μS    |

| Acquisition Time                            | tA             | C <sub>H</sub> = 1000 pF                                                       |        | 20    | 40   | μS    |

| Acquistion Current                          | IA             |                                                                                | 150    |       |      | μА    |

| Ramp Start Delay Time                       | to             |                                                                                |        | 100   |      | ns    |

| Multiplexer Address Time                    | t <sub>M</sub> |                                                                                |        | 1.0   |      | μS    |

| Digital Input HIGH Voltage                  | VIH            | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , ramp start                  | 2.0    |       |      | V     |

| Digital Input'LOW Voltage                   | VIL            | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , ramp start                  |        |       | 0.8  | V     |

| Analog Input Current                        | IB             | Channel ON or OFF                                                              | -3.0   | -1.0  |      | μΑ    |

| Input LOW Current                           | liL            | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , ramp start = 0.4 V          | -15    | -5    |      | μΑ    |

| Input HIGH Current                          | Ін             | $A_0$ , $A_1$ , $A_2$ , ramp start = 5.5 V                                     |        |       | 1.0  | μΑ    |

| Input Offset Current                        | los            |                                                                                |        | 1.0   | 3.0  | μΑ    |

| Comparator Logic "1" Output Leakage Current | Іон            | V <sub>OH</sub> = 15 V                                                         |        |       | 10   | μΑ    |

| Comparator Logic "0" Output Voltage         | Vol            | I <sub>OL</sub> = 1.6 mA                                                       |        |       | 0.4  | V     |

| Power Supply Rejection Ratio                | PSRR           | (Note 3)                                                                       | 40     |       |      | dB    |

| Crosstalk Between Any Two Channels          |                | (Note 4)                                                                       | 60     |       |      | dB    |

| Power Supply Current                        | Icc            | $V_{CC} = 5 \text{ V to } 15 \text{ V}, I_0 = 0$                               |        | 7.5   | 15   | mA    |

| Input Capacitance                           | CIN            |                                                                                |        | 3.0   |      | pF    |

| Comparator Output Capacitance               | Соит           |                                                                                |        | 5.0   |      | pF    |

#### NOTES:

- 1. Conversion accuracy is defined as the deviations from a straight line drawn between the points defined by channel address 000 (0 scale) and channel address 111 (full scale) for all channels.

- 2. Linearity is defined as the deviation from a straight line drawn between the 0 and full scale points for each channel.

- 3. Power supply rejection ratio is defined as the conversion error contributed by power supply voltage variations while resolving mid scale on any channel.

- 4. Crosstalk between channels = 20 log  $\frac{\Delta V_{CH}}{\Delta V_i}$

#### **FUNCTIONAL DESCRIPTION**

This Analog to Digital Converter is a single-slope 8-bit, 6-channel A/D converter that provides all of the necessary analog functions for a microprocessor-based data/control system. The device uses the processor system to provide the necessary addressing, timing and counting functions and includes a 1 of 8 decoder, 8-channel analog multiplexer, sample and hold, precision current reference, ramp integrator and comparator on a single monolithic chip.

For applications that require auto-zero or auto-calibration, (See Figures 2-5) line select address 0, 0, 0 and 1, 1, 1 may be used in conjunction with the arithmetic capability of the microprocessor to provide ground and scaling factors. Address 0, 0, 0 internally connects the input of the ramp generator to ground and may be used for zero offset correction in subsequent conversions. Address 1, 1, 1 internally connects the input of the ramp generator, to the voltage reference, VREF, and may be used for scale factor correction in subsequent conversions. For the following, refer to the Functional Block Diagram.

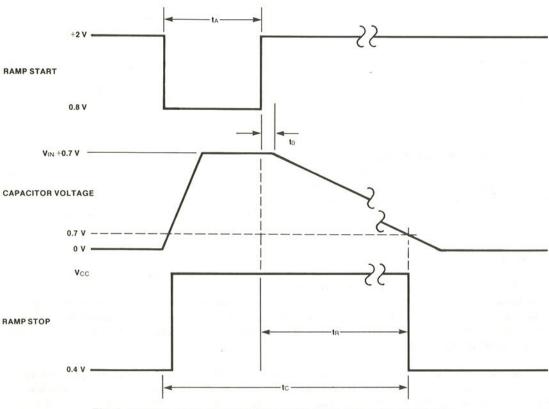

Six separate external analog voltage inputs may come into terminals  $I_1$ - $I_6$  and the specific analog input to be converted is selected via address terminals  $A_0$ - $A_2$ . The analog input voltage level is transferred to the external ramp capacitor connected to pin 4 when the input to the ramp start terminal (pin 3) is at a logic 0 (See *Figure 1*). The time to charge the capacitor is the acquisition time

# FAIRCHILD • µA9708

which is a function of the output impedance of an amplifier internal to the A/D and the value of the capacitor. After charging the external capacitor the ramp start terminal is switched to a logic 1 which introduces a high impedance between the analog input voltage and the external capacitor.

The capacitor begins to discharge at a controlled rate. The controlled rate of discharge (ramp) is established by the external reference voltage, the external reference resistor, the value of the external capacitor and the internal leakage of the A/D. Connected to the capacitor terminal is a comparator internal to the A/D with its output going to the ramp stop terminal (pin 7). The comparator output is a logical one when the capacitor is charged and switches to a logic 0 when the capacitor is in a discharged state. The ramp time is the time from when ramp start goes high (logic "1") to when ramp stop goes low (logic "0"). The microprocessor must be programmed to determine this conversion time. The ideal (no undesirable internal source impedances, leakage paths, errors on levels where comparator switches or delay time) conversion time is calculated as follows.

Ramp Time =

$$V_1 = \frac{C_H}{I_R}$$

Where V<sub>1</sub> = Analog Input Voltage being measured

CH = External Ramp Capacitor

$$I_{R} = \frac{V_{CC} - V_{REF}}{R_{REF}}$$

Where Vcc = Power Supply Voltage

V<sub>REF</sub> = Reference Voltage

RREF = Reference Resistor

In actual use the errors due to a nonideal A/D can be minimized by using a microprocessor to make the calculations. (See Figures 2 through 5)

Fig. 1 Equivalent Timing Waveform for Test Circuits and Applications

# FAIRCHILD • µA9708

#### **APPLICATION HINTS AND FORMULAS**

- 1. The capacitor node impedance is approximately 30  $\mu\Omega$  and should have no parallel resistance for proper operation.

- 2.  $t_R$  when  $V_{IN}=0$  V will be finite (i.e., the comparator will always toggle for  $V_{IN}\geq0$  V.)

- 3. The ramp stop output is open collector, and an external pull up resistor is required.

- 4. All digital inputs and outputs are TTL compatible.

- 5. For proper operation timing commences on the 0 to 1 transition of ramp start and terminates on the 1 to 0 transition of ramp stop.

6.

$$t_A \ge \frac{C_H}{150 \ \mu A - I_R} \ X \ V_{REF}$$

7.

$$t_R$$

(ramp time) =  $\frac{C_H}{I_R}$  X  $V_{IN}$ ,  $t_R$   $|_{max}$  =  $\frac{C_H}{I_R}$  x  $V_{REF}$

8.

$$I_R = \frac{V_{CC} - V_{REF}}{R_{REF}}$$

- 9.  $2 \text{ V} \leq \text{V}_{REF} \leq (\text{V}_{CC} 2 \text{ V})$

- 10. Address lines Ao, A1, A2 must be stable throughout the sampling interval, tA.

- 11. Pin 6 (R<sub>REF</sub>) should be bypassed to ground via a 0.02  $\mu$ F capacitor.

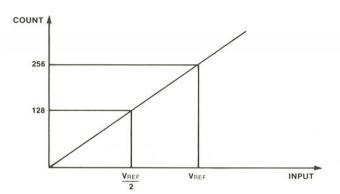

### **AUTO-ZERO AND FULL-SCALE FEATURES**

- NO ZERO OFFSET

- . NO FULL-SCALE ERROR

- COUNT (N) =  $\frac{V_{IN}}{V_{REF}}$  = 256

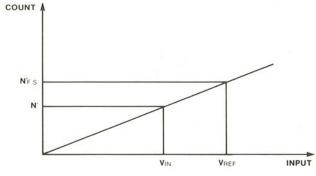

Fig. 2 Ideal Transfer Function

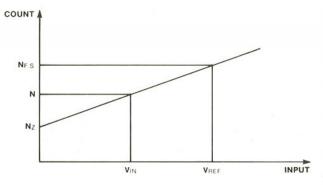

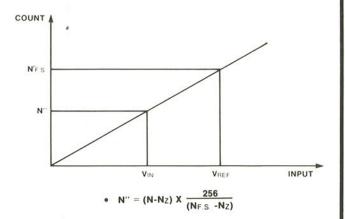

- N<sub>F.S.</sub> ≠ 256

- Nz ≠ 0

- (N) HAS BOTH FULL-SCALE AND ZERO ERRORS

Fig. 3 Transfer Function with Zero and Full-Scale Error

- N' = N -Nz

- . N' HAS FULL-SCALE ERROR

Fig. 5 Both Zero and Full-Scale Correction Added

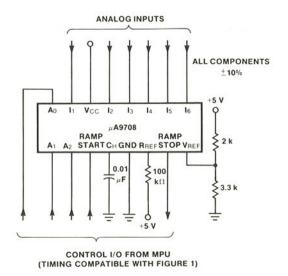

## **TEST CIRCUITS**

INPUT TIMING:

$t_A > 400 \mu s$

$$V_{REF} = \left(\frac{3.3 \text{ k}\Omega}{2 \text{ k}\Omega + 3.3 \text{ k}\Omega}\right) 5 \text{ V} = 3.1 \text{ V}$$

$$I_R = \frac{5-3.1}{100 \text{ k}\Omega} = 19 \mu A$$

$$t_{R}$$

= full scale ramp time =  $\frac{0.01 \times 10^{-6}}{19 \times 10^{-6}}$  X 3.1 = 1.6 ms

#### NOTE:

For evaluation purposes, the ramp start timing generation can be implemented with a  $\mu$ A555 timer (astable operation) or MPU evaluation kit, and a time internal meter for ramp time measurement. The TIM meter will measure the time between the 0 to 1 transition of the ramp start and the 1 to 0 transition of the ramp stop is open collector, and must have an external pull up resistor to V<sub>CC</sub>.

Fig. 6 Slow Speed Evaluation Circuit for Ratiometric Operation

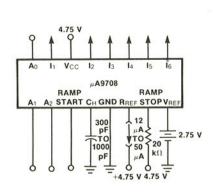

Fig. 7 Linearity/Acquisition Time/Conversion

Time Test Circuit

Fig. 8 Static Measurements

## TYPICAL APPLICATIONS

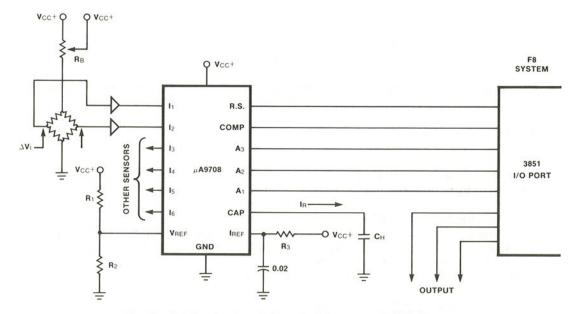

$\Delta V_I =$  (Applied Force) and can be Linearized (if necessary) in F8 Software.

## Ratiometric Strain Gage Sensor/Controller

# APPLICATIONS:

- BEVERAGE BREWERS/DISPENSERS

- . CHEMICAL SOLUTION CONTROL

- AUTOMATIC LIQUID MIXING CONTROL

RAMP CURRENT =

$$I_R = V_{CC} \left( \frac{R_1}{R_1 + R_2} \right) \left( \frac{1}{R_3} \right)$$

$$V_I = \left(\frac{R_X}{R_X + R_B}\right) \, V_{CC} +$$

$$\text{RAMP TIME} = V_1 \quad \frac{C_H}{I_R} \quad = \left( \begin{array}{cc} R_X \\ \overline{R_X + R_B} \end{array} \right) \left( \begin{array}{cc} 1 + \frac{R_2}{R_1} \end{array} \right) \left( \begin{array}{cc} C_H R_3 \end{array} \right)$$

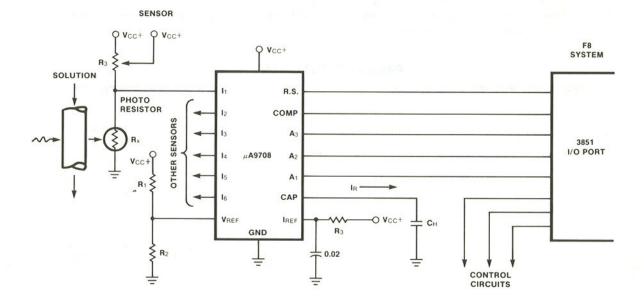

**Opaque Solution Controller**

#### SYSTEM HINTS:

Several alternatives exist from a hardware/software standpoint in microprocessor based systems using the  $\mu$ A9708.

- 1. The ramp time measurement may be implemented in software using a register increment, followed by a branch back depending on the status of the ramp stop.

- 2. Alternately, the ramp stop may be tied into the interrupt structure in systems containing a programmable binary timer. This scheme has the following advantages:

- A. The CPU is not committed during the ramp time interval.

- B. It requires only 4 bits of an I/O port for control signals.

- 3. The auto-zero/auto-full-scale (see *Figures 2-5*) should use double precision, rounded (as opposed to truncated) arithmatics. Several points are worth noting:

- A. The subtractions are single op code instructions.

- B. The full scale correction uses a multiply by 256 and can be accomplished by a shift left 8 bits (usually one instruction) or placing (N-Nz) in the MSB register and setting the LSB register to zero, for the double precision divide.

- C. The divisor (NF.S. Nz) MSB's register will always be zero.

These schemes have the following advantages:

- A. No access to the data buss or address buss is required, by the A/D system.

- B. 4 I/O bits completely support the A/D system.

- C. Since auto full scale/auto zero are implemented in software and long term drift (aging) effects are eliminated.

- D. Software overhead is minimal (typically 30 bytes).

- E. Where ratiometric operation is permissible, the 4 external components may be  $\pm 5\%$  tolerance, including the power supply.

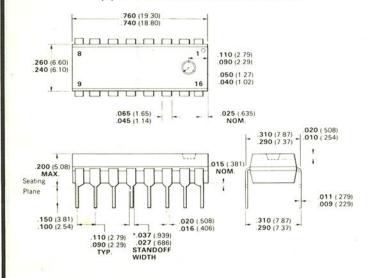

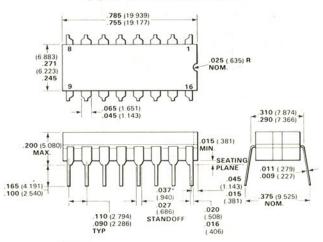

### **PACKAGE OUTLINES**

#### (P)9B 16-PIN MOLDED DUAL IN-LINE

#### (D) 7B 16-PIN HERMETIC DIP

#### NOTES:

All dimensions in inches (bold) and millimeters (parentheses)

Pins are intended for insertion in hole rows on .300" (7.62) centers

Board-drilling dimensions should equal your practice for .020" (0.508) diameter pin \*The .037/.027 dimension does not apply to the corner pins

Package weight is 0.9 gram

NOTES:

All dimensions in inches

Pins are tin-plated 42 alloy

Pins are intended for insertion in hole rows

on .300" (7.62) centers

They are purposely shipped with "positive"

misalignment to facilitate insertion

Board-drilling dimensions should equal

your practice for .020 (0.51) inch diameter

pin

Hermetically sealed alumina package

"The .037-.027 (0.94-0.69) dimension does

not apply to the corner pins

Package weight is 2.2 grams